# Signal Transmission and Correlator

- Our engineering limitations

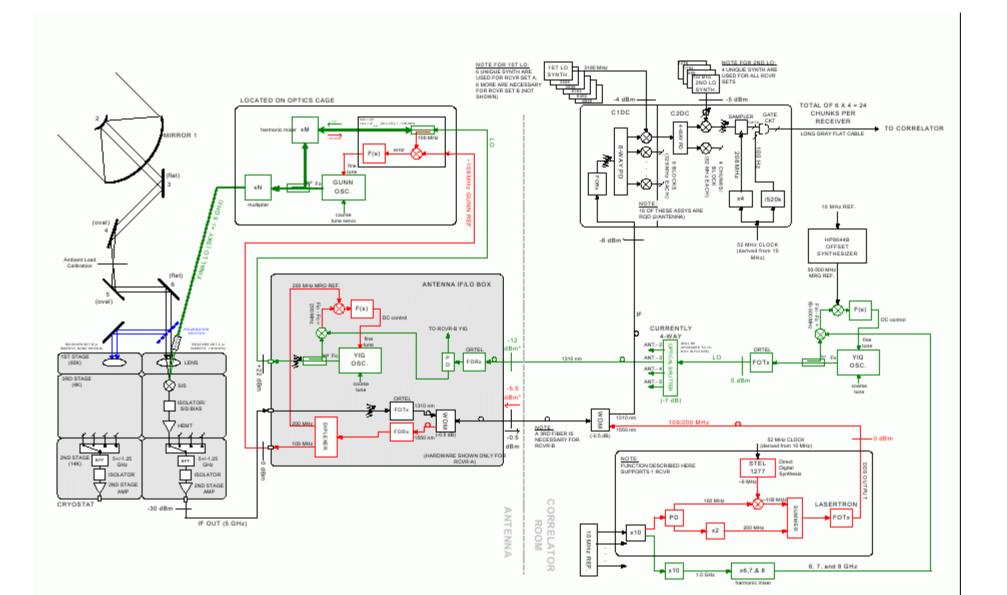

- The present SMA system

- Analog IF and transmission upgrades

- New correlator options

- What we want

- Available A/D converters

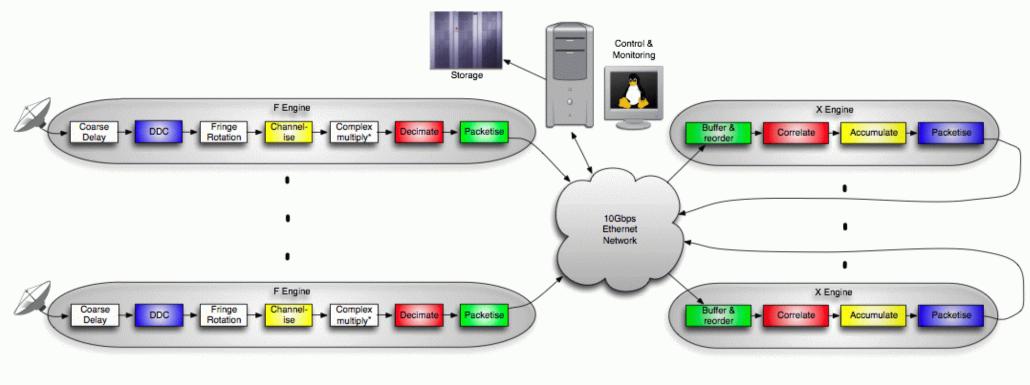

- The CASPER approach

- Custom backplane corner turning

- Commercial vendors

| feature                         | full offering        | initial release | remarks                               |

|---------------------------------|----------------------|-----------------|---------------------------------------|

| number of antennas              | 8                    |                 | 2 Rx each. eSMA support?              |

| total bandwidth                 | 18 GHz               | 9 GHz           | for each of two receivers             |

| number of sidebands             | 2                    |                 | upper and lower 18 GHz each           |

| simultaneous receivers          | 2                    | 1               | dual freq. or dual pol. 230 & 345 GHZ |

| # baselines                     | 56                   | 28              | 28 per Rx, full Stokes                |

| finest continuum resolution     | $0.5 \ \mathrm{MHz}$ |                 | 16,384 channels / 9 GHz block         |

| coarsest continuum resolution   | 70.3  MHz            |                 | 128 channels / 9 GHz block            |

| finest spectral line res.       | 25  kHz              |                 | best possible SMA res                 |

| # spectral bands                | 12                   |                 | maximum simultaneous hires bands      |

| zooming band width              | 500  MHz             |                 | widest single spectral line           |

| fastest dump rate               | $0.65 \ s$           |                 | single full Walsh cycle               |

| dynamic range                   | 30  dB               |                 | weak spectral line near strong        |

| baseline to baseline isolation  | 30  dB               |                 | crosstalk from baseline to baseline   |

| sideband isolation              | 25  dB               |                 | crosstalk USB <> LSB                  |

| maximum baseline delay          | 2  km                |                 | assumes current SMA configuration     |

| # simultaneous autocorrelations | 16                   |                 | Can autocorrelate each antenna        |

| phased array bandwidth          | 8 GHz                | 4 GHz           | 4 GHz $\times$ dual pol.              |

| celestial holography mode       |                      |                 | might need faster dump                |

${\bf Table \ 1.} \ {\rm User \ requirements \ for \ SMA \ wideband \ correlator.}$

| $f_s (\text{GSa/s})$ | BW (GHz) | # bits       | Manuf.   | Part $\#$          | $\sim \! \mathrm{cost}$ | remarks                    |

|----------------------|----------|--------------|----------|--------------------|-------------------------|----------------------------|

| 5                    | 2.0      | 8            | e2v      | EV8AQ160           | \$300                   | ASIAA board H. Jiang       |

| 12.5                 | 8        | 8            | Maxtek   |                    | 17k                     | mature module              |

| 20                   | 8        | 5            | $e^{2v}$ | EV5AS210           | $^{\rm $7k}$            | Torres et al., IRAM, 8Gsps |

| 20                   | 13       | 8            | Agilent  |                    |                         |                            |

| 26                   | 26       | 3+ of<br>low | Hittite  |                    | 8k                      | 'rumored' @ $\sim$ \$8k    |

| 30                   | 14       | 6            | Micram   | ADC30              | \$10k                   | only demo 12 $GSa/s$       |

| 56                   | 15       | 8            | Fujitsu  | CHAIS              |                         | snapshot, no stream        |

| 20                   | 10       | 1            | Hittite  | HMC874LC3C         | \$40                    | clocked comp, no demux     |

| 12.5                 | 14       | 1            | Inphi    | $1385 \mathrm{DX}$ |                         | latched comp, 1:8 demux    |

| 25                   | 18       | 1            | Inphi    | 25707 CP           |                         | latched comp, no demux     |

| ADC Sample<br>Rate | Chunk Width | # Chunks per<br>antpol | Total Chunks |

|--------------------|-------------|------------------------|--------------|

| 5                  | 2           | 9                      | 144          |

| 10                 | 4.5         | 4                      | 64           |

| 14                 | 6           | 3                      | 48           |

| 20                 | 9           | 2                      | 32           |

#### Our current IF processor has 384 chunks

#### CASPER

\*Complex multiply allows for fine delay control and per-channel digital gain control. White coloured blocks not yet implemented.

- One 10GbE will carry ~ 8 Gb/s, at 4 bits/sample -> 2Gs/s or 1 GHz

- There could be 19 separate 10GbE switches

- Each switch would have 16 inputs (using a standard trick of feeding the F engines through the X engines to exploit the bidirectionality of the ports).

- Total 608 ports @ \$200/port -> \$1.2M

### Specialized Backplane for Corner Turning

- This is the approach CARMA and PdBI are using.

- A Vertex 6 has a large number of LVDS ports which can be routed in a backplane.

- Each backplane would need to support 16 station cards and some number of X engines.

- There would be 2-9 back planes depending on the ADC sampling rate.

- In the case of 9 analog channels there might be only 9 station cards.

## Summary

- We have limited ability to design high speed digital cards or produce large numbers of Analog channels.

- The situation with high speed A/D converters is unclear now, but several are promised.

- The CASPER approach is appealing. It is being used by other large projects (MeerKat and PAPER).

- For large systems a more custom system design such as Dave Hawkins is doing may be advantageous. We are looking into what he is doing. His designs are motivated by reusing existing hardware, though.

- There are companies who design systems with state of the art FPGAs. We are talking to one.

- See more on the poster by Jonathan Weintroub and Rurik Primiani in the control room or ask for a lab demo.